#### Computer Science CSCI 355

#### Digital Logic and Computer Organization

Dr. Peter Walsh

Department of Computer Science

Vancouver Island University

peter.walsh@viu.ca

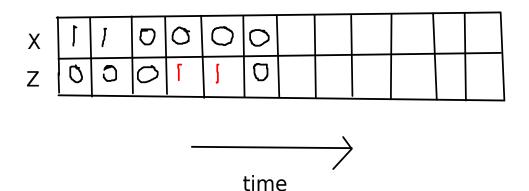

#### Non Resetting Sequence Detector

Task: design and construct a non-resetting sequence detector to detect the sequences 1100 or 1000 using D edge triggered flip flops.

One input X. One output Z.

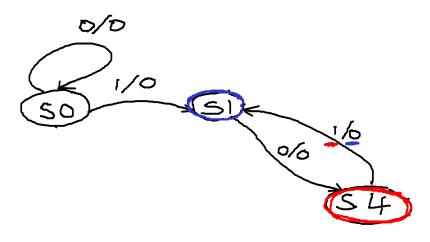

### State Table Construction (Step 4)

| Present State | Next State | e Out      | Output |   | Encoding |    |  |

|---------------|------------|------------|--------|---|----------|----|--|

| Q             | Q+         | <b>-</b> ≺ | Z      |   | QB       | QC |  |

|               | X=0 $(X=$  | X=0        | X=1    |   |          |    |  |

| S0            | S0 S       | 1 0        | 0      | 0 | 0        | 1  |  |

| <b>S</b> 1    | S4         | 0          |        | 1 | 0        | 1  |  |

| <u>S4</u>     | S          | 1)         | 0      |   |          |    |  |

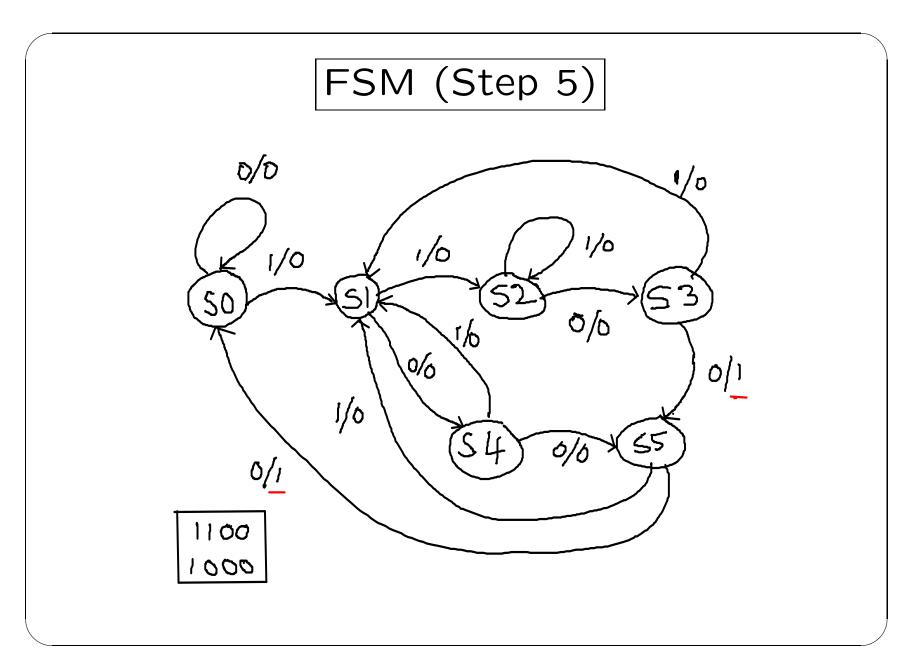

# State Table (Step 4)

| Present State | Next S     | State     | Output |     | Encoding |   |   |

|---------------|------------|-----------|--------|-----|----------|---|---|

| Q             | Q+         |           | Z      |     | QA QB QC |   |   |

|               | X=0        | X=1       | X=0    | X=1 |          |   |   |

| <b>S</b> 0    | S0         | S1        | 0      | 0   | 0        | 0 | 1 |

| S1            | <b>S</b> 4 | <b>S2</b> | 0      | 0   | 1        | 0 | 1 |

| <b>S2</b>     | <b>S</b> 3 | <b>S2</b> | 0      | 0   | 1        | 1 | 1 |

| <b>S</b> 3    | S5         | S1        | 1      | 0   | 0        | 1 | 0 |

| <b>S4</b>     | S5         | S1        | 0      | 0   | 0        | 1 | 1 |

| S5            | <b>S</b> 0 | S1        | 1      | 0   | 0        | 0 | 0 |

5: Computer Science CSCI 355 — Lecture 20

# State Table cont. (Step 4)

| QA QB QC      |            |     |        |    |

|---------------|------------|-----|--------|----|

| Present State | Next State |     | Output |    |

| Q             | Q+         |     | Z      |    |

|               | X=0        | X=1 | X=0 X  | =1 |

| 001 50        | 001        | 101 | 0      | 0  |

| 101 51        | 011        | 111 | 0      | 0  |

| 111 52        | 010        | 111 | 0      | 0  |

| 010 53        | 000        | 101 | 1      | 0  |

| 011 54        | 000        | 101 | 0      | 0  |

| 000 55        | 001        | 101 | 1      | 0  |

|               | I          |     |        |    |

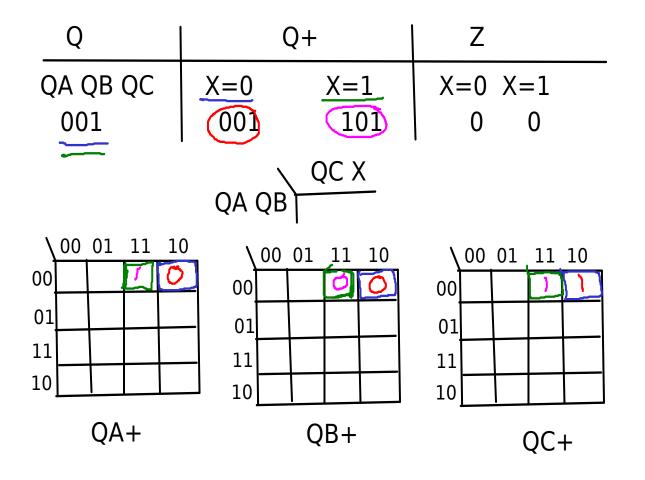

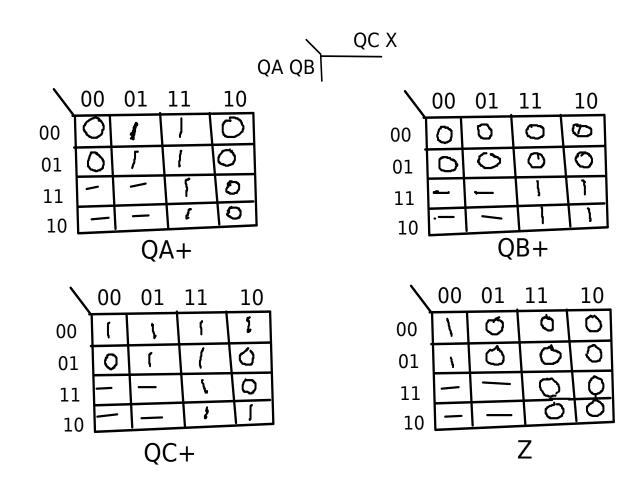

## K Map Construction (Step 3)

7: Computer Science CSCI 355 — Lecture 20

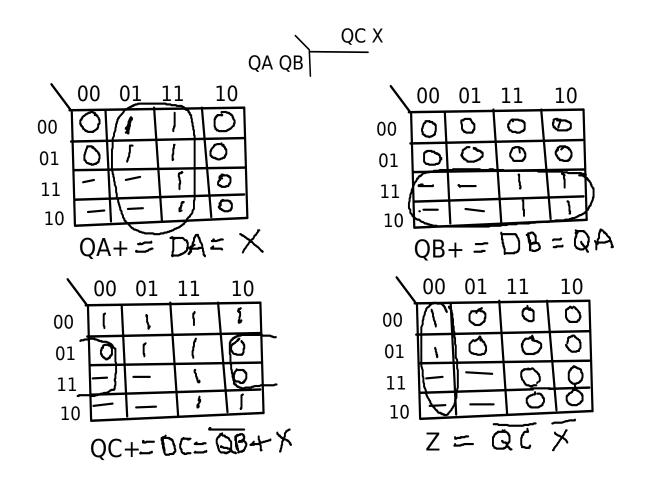

### K Map Construction (Step 3)

#### Excitation Tables)

### FF-Input And Output Eq. (Step 2)

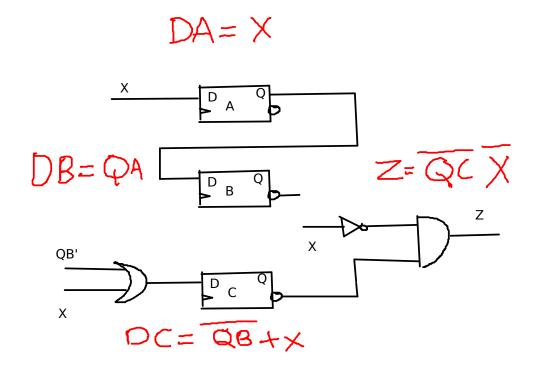

### Circuit Diagram (Step 1)

11: Computer Science CSCI 355 — Lecture 20